1.项目原理图

本项目电路图采用模块化绘制,在电路图中对不同模块使用线条进行了分区以便于读图,下面将分模块对电路图进行分析。

2.电路分析

1、供电电路

LDO(低压差线性稳压器)选型

本项目使用LDO作为电源,考虑到实际的电压表头产品多在24V或36V供电的工业场景中应用,本项目选择了最高输入电压高达40V的SE8550K2作为电源。本项目没有使用DCDC降压电路来应对大压差的主要原因为避免设计过程中引入DCDC的纹波干扰,次要原因为降低项目成本。

封装选型

从数据手册截图的表格中,可以看出,同SOT23封装的280℃/W相比,SOT89封装的165℃/W有更好的散热能力(Thermal Resistance,Junction-to-Ambient),单位:摄氏度/瓦。

LDO型号选择

由于项目的主控核心板为5V供电,所以根据下表订购信息描述,选择SE8550K2-HF,输出5V,K即为SOT89封装,±2%精度即可,省成本。HF或LF与环保要求有关,在实际产品设计中需关注。本项目无需关注。

电容器的设计

手册中给出了该LDO的应用原理图:

几乎所有的LDO器件,在设计电路时的原理是基本一致的。所以这张图的参考意义,并不是很大,而往往不一样的考量,是C1、C2应当如何设计,如果你的LDO有EN(enable),还需额外考虑使能引脚的设计,保证芯片正常工作。此外,还有些LDO是可调输出的,他有一个专门的引脚(adj),需要配置相应的外围电阻器来实现输出指定的电压。

而LDO外围电路设计,最核心的是电容器的设计。

LDO外围的电容器在电路中扮演着关键的角色,其作用主要包括以下几个方面:

- 滤波作用 :LDO外围的电容器,特别是输入电容,能够有效地滤除前级电源带来的纹波干扰。

- 改善负载瞬变响应 :输出电容在改善负载瞬变响应方面起着重要作用。当负载电流急剧变化时,LDO存在调整时间,此时输出电容作为临时电源,为电路提供所需的电流,防止输出电压被拉得过低。较大的输出电容值可以进一步改善LDO对大负载电流变化的瞬态响应。

- 相位补偿 :对于可调输出的LDO,并联在上电阻(R1)的电容器(称为反馈电容器CFB)提供超前相位补偿,增加振荡裕度并改善负载瞬态响应。CFB和R1归零,有助于环路稳定性。

- 防止振荡 :适当的电容器配置可以帮助防止LDO电路中的振荡现象,确保电路的稳定运行。

- 纹波抑制 :电容器在LDO中也有助于提高纹波抑制比(PSRR),即电源抑制比,减少电源噪声对电路性能的影响。

- 启动浪涌电流控制 :输入电容在LDO启动过程中充当启动浪涌电流的临时电源,防止输入电压被拉低,影响前级电源稳定性。

归纳:LDO外围的电容器在滤波、改善负载瞬变响应、相位补偿、防止振荡、纹波抑制和启动浪涌电流控制等方面都发挥着重要作用。通过合理配置这些电容器,可以确保LDO电路的稳定性和性能。

如果你认真的翻阅了数据手册,就会发现官方已经给了一些详细的建议和参考,还有Layout设计建议。这避免了工程师去做大量理论计算的复杂工作。

值得注意的是,我在电源设计中,使用电解电容和陶瓷电容前后顺序并联的方式设计。当电解电容和陶瓷电容并联时,它们能够“高低搭配”,使得电路在高频和低频区域都具有较好的滤波作用。电解电容滤除低频干扰,而陶瓷电容滤除高频干扰,两者结合可以获得更好的滤波效果。

在实际电子产品中,电解电容并联陶瓷电容的主要作用是通过两者的互补特性,实现高低频滤波和耦合作用,从而改善电路性能,提高稳定性和抗干扰能力。这种并联方式在电子设备中得到了广泛应用。

扩展知识: 电解电容和陶瓷电容前后顺序并联

- 当电解电容和陶瓷电容并联使用时,电解电容首先过滤掉输入电压中的低频部分,为电路提供稳定的直流电压。这有助于确保电路在低频时的稳定性和可靠性。

- 随后,陶瓷电容进一步补偿高频波动,滤除高频噪声和脉冲危害。这种高低搭配的滤波方式能够更有效地滤除整个频段的噪声和波动,提高电路的整体性能。

- 此外,陶瓷电容还可以消除电解电容在高频时产生的感性特性(电容的寄生电感),进一步提高滤波效果。

新手在试图理解电容的隔直、耦合、旁路、滤波、调谐回路、能量转换、控制等作用时,应先返璞归真,理解电容器的本质:电容器用于存储电荷和电能,并能够在电路中释放这些存储的电荷。

提前简单讲一下,MCU外围的电容器为何要就近放置:远水救不了近火。MCU等器件在使用电的时候,线路上的电流值可能是突变的,有时为了维持MCU上突变的电流(即电荷的定向移动形成的物理量)的需求,需要就近的电容释放电荷。

电流的大小反映了单位时间内通过导体横截面的电荷量,描述电路中电荷运动状态的重要物理量。

二极管防反接

考虑到高电压反接将会给模块带来不可逆的损坏,电压表头供电电路采用了串联二极管的方案进行防反接。

注:本项目使用串联二极管进行防反接考虑到了本设备供电电压通常高于5V的使用场景,二极管的0.7V压降将不会供电造成影响。当供电电压较低时,由于项目的总体功耗较低,实测供电电流较低(20mA),由于肖特基二极管 D4(1N5819)独特的结构,相比于通用开关二极管等,VF更低,由下图可见,压降约为0.2V以内。

常规的电路设计中,使用反向并联二极管+串接保险丝的方案也可达成防反接和电路保护目的。

串联小电阻(10Ω)的作用

本项目额外使用了串联小电阻(10Ω)来进行分压操作,一方面减少在高电压情况下LDO由于较大的压差导致发热严重的问题。另一方面,利用了串联的10欧姆小功率电阻过电流小的原理,充当低阻值保险丝,具有电路过流保护或者短路保护作用。(电阻做保险丝这个点,因为电阻在过流状态,处于发热状态,99%都是开路,它基本不会短路。它的故障分析就决定了它基本上以开路为主。也就是烧断掉,不会短在一起。)

串联的小电阻(10Ω)还可降低上电冲击的峰值,避免冲击过高损坏LDO。

如果没有使用电解电容,串联的小电阻(10Ω)也可避免热插拔的时候,导线电感和陶瓷电容形成谐振,因为陶瓷电容具有非常小的ESR,导致LC网络中的阻尼很少,谐振点的增益会很高,加入外部电阻提供阻尼后就可以抑制谐振点的增益。

电路设计要点及规范

在电源电路绘制时,无论是原理图还是PCB,应当注意几点问题:

原理图规范性:GND朝下,电源在上,不要出现地朝天的情况。

电容器设计:无论原理图还是PCB,电解电容在前,陶瓷电容在后

地线设计:单点接地,当前电源的地,汇总到当前电源的主电解电容的GND上,各级电源的主电解电容,汇总到前级电源的主电解电容的GND上。

扩展知识:PCB设计的单点接地

PCB设计的单点接地是指在PCB线路板上只有一个地点与整个系统的地相连接。这意味着所有的电路地线都将连接到这个公共的接地点上,形成一个统一的接地系统。 PCB设计的单点接地是一种重要的电路设计技术,其主要目的是为了简化电路设计,提高系统的稳定性和抗干扰能力。

单点接地的好处:

- 简化电路设计:单点接地可以大大简化电路设计,减少连接线路的长度和复杂性,降低电磁干扰的可能性。

- 提高系统稳定性:通过单点接地,可以更好地控制接地回路的大小,减少接地环路对信号传输和系统稳定性的影响,从而提高系统的稳定性和可靠性。

- 降低噪声和干扰:单点接地可以减少信号和电流的回流路径,降低系统中产生的回流噪声,提高信号传输的质量和可靠性。

- 减少地环路产生:单点接地可以有效减少接地环路的产生,避免产生接地回路的非线性效应,降低系统中产生的干扰和噪声。

在PCB设计中,单点接地可以通过以下几种方式实现:

- 串联单点接地:将各个需要接地的点通过一条公共的地线串联起来,然后接到公共接地点上。这种方式简单易行,但地线长度较长时可能会引入较大的阻抗。

- 并联单点接地:将各个需要接地的点分别通过短的地线直接接到公共接地点上。这种方式可以减小地线阻抗,但可能需要更多的接地点和更复杂的布线。

- 混合接地:将电路按照信号特性分组,相互不会产生干扰的电路放在一组,一组内的电路采用串联单点接地,不同组的电路采用并联单点接地。这种方式可以灵活应对不同电路的需求,提高系统的整体性能。

注意事项:

- 选择合适的接地点:接地点应该选择在电路板上电位最稳定的点,通常选择在电源滤波电容的负极附近。

- 控制地线长度:地线长度应该尽量短,以减小地线阻抗和引入的噪声。

- 避免地环路:在设计过程中应该尽量避免形成地环路,以减少地环路产生的噪声和干扰。

- 分开处理数字和模拟信号:由于数字信号变化速度快,容易在数字地上产生噪声,因此应该尽量将模拟地和数字地分开处理,减少它们之间的干扰。

综上所述,PCB设计的单点接地是一种重要的电路设计技术,它可以通过简化电路设计、提高系统稳定性和降低噪声干扰等方式提高电路的整体性能。在实际应用中,需要根据具体的系统需求和性能要求来选择合适的单点接地实现方式,并注意控制地线长度、避免地环路和分开处理数字和模拟信号等问题。

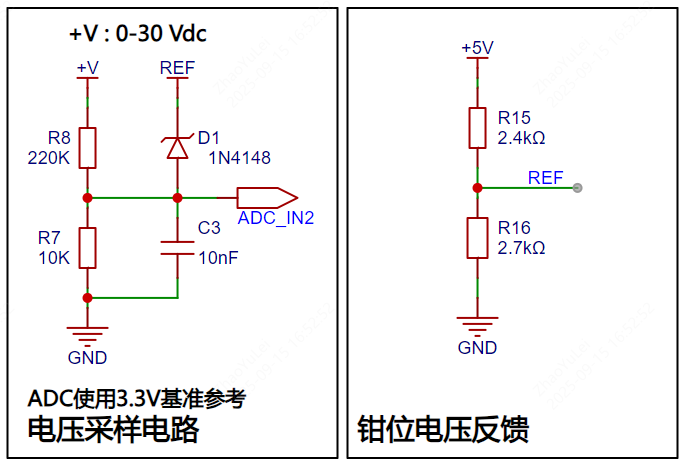

2、电压采样电路

本项目采用分压电路实现高电压采集,理论上设计可采集电压100V,实际

只允许输入采集电压为0-30V。

只允许输入采集电压为0-30V。

只允许输入采集电压为0-30V。

重要的事情说三遍。

本项目设计分压电阻为220K+10K,因此分压比例为22:1(ADC_IN11)

分压电阻选型

设计测量电压的最大值,出于安全考虑,本项目为30V);

ADC参考电压,本项目中为3.3V,该参考电压可以通过程序进行配置;

功耗,为了降低采样电路的功耗,通常根据经验值将低侧电阻(R7)选择为10K;

随后便可以通过以上参数计算出分压电阻的高侧电阻:

计算所需的分压比例:即ADC参考电压:设计输入电压,通过已知参数可以计算出3.3V/30V=0.11

计算高侧电阻:即低侧电阻/分压比例,通过已知参数可以计算出10K/0.11=90K

选择标准电阻:选择一颗略高于计算值的电阻,计算值为90K,通常我们选择E24系列电阻,因此本项目中选择大于90K,实际上我们还是使用220K。

注:为了方便大家直接复刻这边的阻值参考CW32电压电流表的阻值不变。

如果在实际使用中,需要测量的电压低于2/3的模块设计电压,则可以根据实际情况更换分压电阻并修改程序从而提升测量的精度,下面将进行案例说明:

假设被测电压不高于24V,其他参数不变

通过计算可以得到3.3V/24V=0.1375,10K/0.1375=72.8K,72.8K为标准E24电阻可以直接选用,或适当留出冗余量选择更高阻值的100K

考虑到被测电源可能存在波动,在电路设计时,在低侧分压电阻上并联了10nF的滤波电容提高测量稳定性。

二极管钳位保证MCU安全

我在设计本项目的时候,额外在采样电路中增加了一个1N4148(D1等)作为钳位二极管。尽可能避免在学习和调试使用中由于接入不正确的电压,导致芯片引脚损坏。二极管钳位是一种重要的电子电路设计技术,它的主要作用是通过限制电压的幅度来保护电路,避免信号过大或过小导致的损坏或故障。

钳位在电路中是指限制电压的意思,而二极管钳位特指利用二极管将电路中的某点电位进行限制的技术。

二极管钳位主要利用了二极管的单向导电性。当二极管的正极电压大于负极电压并且导通后,二极管两端的电压被限制在其管压降上,通常硅管的管压降约为0.7V。

钳位过程:通过二极管的钳位作用,将被钳位的电位强制拉向参考端,从而实现电位的限制。钳位并不改变原信号的波形,只是抬高或降低了信号的基准电位。

根据二极管连接方式的不同,钳位电路可分为正向钳位电路和负向钳位电路。本项目仅设计了正向钳位。

- 正向钳位电路:当二极管的正极接地时,为正向钳位电路。在正半周时,二极管截止;在负半周时,二极管导通,电容被充电至一定电压,使输出电压限制在一定范围内。

- 负向钳位电路:当二极管的负极接地时,为负向钳位电路。工作原理与正向钳位电路相反。

注:地奇星ADC的IO口最高只能承受3.3V的电压值。故此需要修改钳位电压,为了不影响ADC的采样值故此需要一个大概2.6V限位电压,故此ADC的IO才能被限制到3.3V。如果接入采样电压小于30V,所以钳位电压没有实际作用。

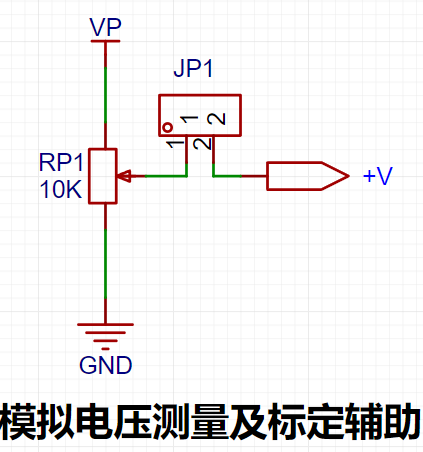

用来模拟电压的测量、测量的标定、和测量校准辅助的电路

用来模拟电压的测量、测量的标定、和测量校准辅助电路

旁边标注为:T_V、T_GND的器件为开发板上的2mm香蕉座接口,用来连接万用表表笔。可插入万用表或高精度台式数字万用表的表笔探头验证开发板测量是否准确。也可插入2mm香蕉头的万用表表笔,代替CH1端口,进行手持式测量。

VP引脚为开发板供电引脚,在使用DC端口时,不接。在没有使用DC端口供电,且测量值大于5V小于30V时,可接入被测电源,也可由此独立供电。

在学习相应电路测量原理时,考虑到用户可能无法便捷的搭建测试和调试的外围电路,本着开发板易于开发的原则,特设置用来模拟电压的测量、测量的标定、和测量校准辅助电路。无需使用CH1外接电压。使用多圈可调电位器(RP1)对开发板电源电压进行分压,通过开发板内部电路连接入+V网络。此时注意,需要短接JP1,使用跳线帽即可,推荐使用长柄跳线帽。不使用此功能,请勿短接JP1。

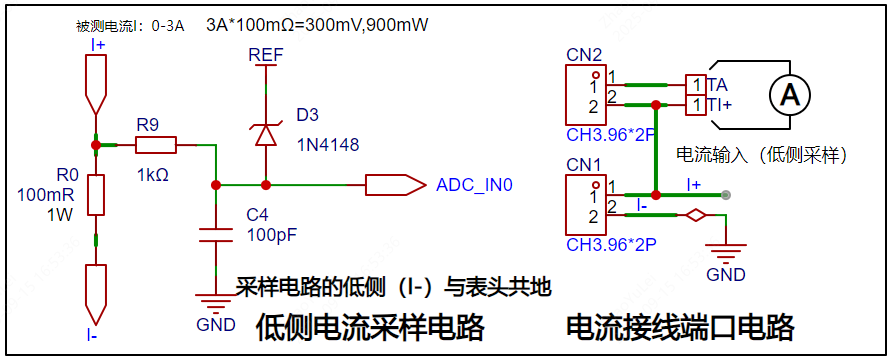

3、电流采样电路

本项目采用低侧电流采样电路进行电流检测,采样电路的低侧与开发板表头接口共地

学习时,请不要焊接R0!!!

设计分析:

本项目设计的采样电流为3A,选择的采样电阻(R0)为100mΩ

只允许输入采集电流为0-3A。

只允许输入采集电流为0-3A。

只允许输入采集电流为0-3A。

重要的事情说三遍

注:V1.2版本的PCB板的ADC输入通道丝印标注错误,请参考按照实际通道使用,不影响其功能。

采样选型主要需要参考以下几个方面:

- 预设计测量电流的最大值,本项目中为3A

- 检流电阻带来的压差,一般不建议超过0.5V

- 检流电阻的功耗,应当根据该参数选择合适的封装,本项目考虑到大电流时的功耗(温度)问题,选择了1W封装的金属绕线电阻

- 检流电阻上电压的放大倍数:本项目中没有使用运放搭建放大电路,因此倍率为1

随后便可以通过以上参数计算出检流的阻值选择:

- 由于本项目没有使用放大电路,因此需要选择更大的采样电阻获得更高的被测电压以便于进行测量

- 考虑到更大的电阻会带来更大的压差、更高的功耗,因此也不能无限制的选择更大的电阻

- 本项目选用了1W封装的电阻,对应的温升功率为1W

综合以上数据,本项目选择了100mΩ的检流电阻,根据公式可以计算出3A*100mΩ=300mV,900mW

如需应对不同的使用环境,尤其是电流较大的场景,可以将R0电阻更换为康铜丝或者分流器,可以更具实际使用场景,选择替代。出于安全和学习用途考虑,本项目对超出3A量程不做过多探讨,但原理一致。

串联1K电阻(R9)的作用

- 保护ADC引脚:

- 在ADC引脚前串联电阻可以起到一定的限流作用,防止在特殊情况下(如高电压输入或短路)电流过大而损坏ADC引脚。

- 减少瞬态电流对ADC转换器性能的影响。

- 滤波和降噪:

- 电阻与ADC引脚后端的电容可以构成一个RC低通滤波器,有助于减缓信号的快速边沿,降低高频噪声对ADC采样的影响。

- 在高精度应用中,这种滤波效果对于提高信噪比(SNR)和确保测量准确性至关重要。

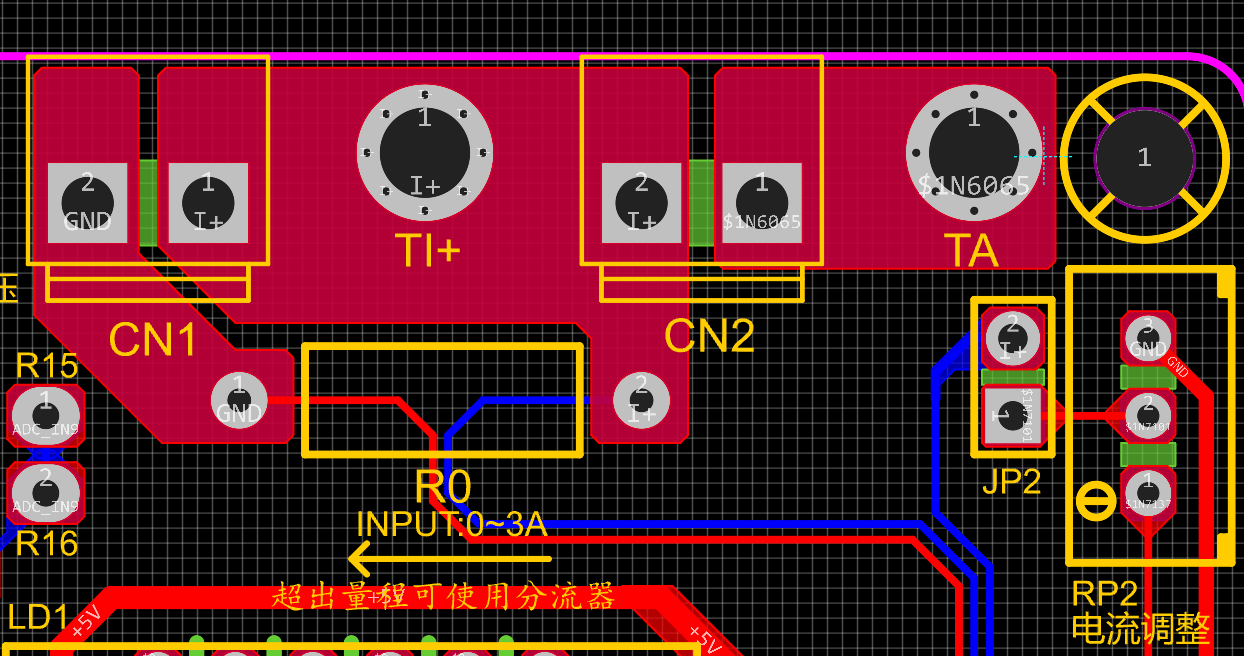

PCBLayout注意事项

在PCB进行Layout也需要特别注意,虽然I-网络与GND网络在电气上为同一网络,但是需要注意的是I-会有大电流通过,属于“功率地”,即使该点已经接地也会因为电流的波动造成网络电平变化,因此我们可以将该网络视为一个“干扰源”;而GND网络为表头电源负极,即“信号地”,同时,由于单片机的AGND与表头GND并未进行隔离,那此时可以将表头GND视为“敏感地”,因此需要避免被干扰。在电路设计中,切勿将所有的GND笼统的连接在一起。这也是在设计该项目时,并未铺铜的原因。

在上图中,黄色箭头标注的即为大电流流通路径,通过接口的I+流入、流经采样电阻、通过接口的I-流出。此时有小伙伴可能会疑惑,为什么我设置了CN1\CN2两个电流采样接口?

电流采样是串联进被测电路的,设置两个接口是为了应对我们的调试(即开发板学习需求)。正常测量仅需接入CN1即可。当项目中需要串联进万用表等设备进行对比验证时,需要同时用CN2的1脚(红线-电流in)和CN1的2脚(黑线-电流OUT)

题外话:若觉得同时使用两个端子太麻烦,在电路设计时,请将CN2的2脚网路,由I+改为GND 。此时,正常测量仍仅需接入CN1即可,而当项目中需要串联进万用表等设备进行对比验证时,仅需要接入CN2。

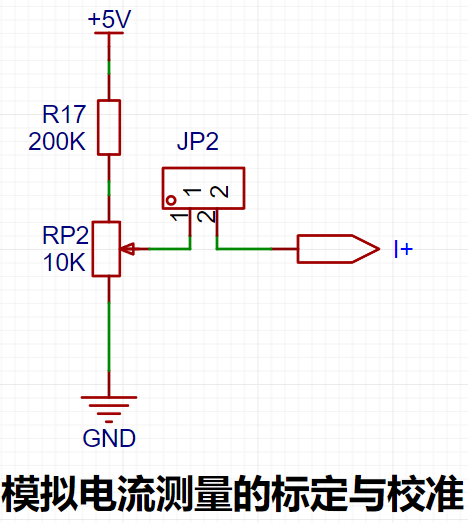

用来模拟电流的测量、测量的标定、和测量校准的辅助电路

用来模拟电流的测量、测量的标定、和测量校准辅助电路

使用此功能时,请不要焊接R0采样电阻。不使用此功能,请断开JP2。

电流采样的实质,是采集采样电阻流过电流时电阻两端的电压降,即采集电压值。该电路使用RP2提供了一个在0~0.238V(5V÷210K*10K)范围内的电压值,经由I﹢网络,接入到芯片用于电流采样的引脚上。

在实际使用时,I﹢处的电压,模拟成了不焊的那个100mΩ采样电阻的电压降,此时,模拟测得的电流值I测=该电压值Vi+ ÷ 100mΩ 也正巧等于测得电压数值乘以10。即,提供了模拟出0~2.38A的电流测量。

将万用表或高精度台式数字万用表调至电压测量端口,量程3V以内。将其表笔探头,黑色负极插入电压测量端子旁的T_GND接口,红色正极表笔插入电流测量的 TI+ 端口,即可测量I﹢的实际电压值。由此可见,该电路可以除了可以完成上述设计任务,也可以直观通过测试体验到MCU的ADC外设的精度。可以自行编写程序进行验证。

4、数码管驱动

本项目采用了数码管作为显示单元。

在本项目中使用了两颗0.28寸的三位共阴数码管作为显示器件,相较于显示屏,数码管在复杂环境中拥有更好的识别度,可以根据实际使用环境的需求,改为更小的限流电阻实现更高的数码管亮度;在另一方面,数码管拥有较好的机械性能,不会像显示屏一样容易被外力损坏。在工业等有稳定可靠性应用中,多被采用。从开发版学习的角度来看,更易有目的的学习电子测量原理相关开发。

在本项目中,经过实际测试,数码管的限流电阻(R1~R6)被配置为300Ω,对应的亮度无论是什么颜色的数码管,均具有较好的识别度,且亮度柔和不刺眼。

严格来讲,限流电阻应该加在段上,加在位上,会影响显示效果。我们实际设计加在位上,省几个电阻,但对显示影响并不突出。所以还是加在位上,图个方便。

数码管的驱动原理

数码管的驱动原理主要涉及到通过控制数码管的各个灯段的开关状态来显示数字、字母或符号。以下是详细的驱动原理说明:

数码管的基本构成:

- 数码管通常由七段或八段LED(本项目为8段)组成,每个段代表数码管的一部分,可以显示数字0-9、字母A-F等字符。

- 数码管有共阴极和共阳极两种类型,它们的区别在于LED的公共端COM(即连接所有LED的一端)是连接到电源的负极还是正极。

驱动方式:

- 段选:通过控制数码管的各个灯段的开关状态来显示所需的数字或字符。每个灯段对应一个控制信号,当控制信号开启时,该段会显示点亮,反之则灭掉。(a、b、c、d、e、f、g、dp)

- 位选:通过控制数码管的位线来选择需要显示的数码管。位线控制是将需要显示的数码管的位线设置为高电平,其他数码管的位线设置为低电平。通过不断地切换位线的状态,可以实现多个数码管之间的显示切换。

驱动电路:

- 数码管驱动电路可以通过硬件电路实现,如使用数字信号处理器(DSP)、微控制器(MCU)或移位寄存器等集成电路来生成适合LED的控制信号。

- 这些控制信号可以是脉冲宽度调制(PWM)信号、串行数据信号等形式。通过控制这些信号的频率、宽度和幅度,可以实现数码管的亮暗控制,从而显示出所需的数字或字母。

软件控制:

- 除了硬件驱动电路,还可以通过软件控制来实现数码管的驱动。通过编程生成适合数码管的控制信号,可以实现更加灵活和复杂的显示效果,如数字的滚动显示、交替显示等。

共阴极与共阳极数码管的驱动:

- 对于共阴极数码管,共阴极引脚连接到电源的负极,控制引脚连接到控制芯片的输出引脚。当需要显示某个数字时,控制芯片会输出相应的编码信号到控制引脚,使得对应的LED段点亮。

- 对于共阳极数码管,工作原理与共阴极数码管相似,只是共阳极引脚连接到电源的正极,控制引脚连接到控制芯片的输出引脚。

编码显示:

- 为了使数码管显示出相应的数字或字符,必须使段数据口输出相应的字形编码。例如,要显示数字“0”,共阳极数码管的字型编码为11000000B(即C0H),而共阴极数码管的字型编码为00111111B(即3FH),具体编码以实际数码管为准。

动态显示与静态显示:

- 数码管可以采用静态显示或动态显示方式。静态显示时,每个数码管的8个字段分别与一个8位I/O口地址相连,I/O口只要有段码输出,相应字符即显示出来并保持不变。动态显示则是一位一位地轮流点亮各位数码管,通过快速切换实现人眼视觉上的同时显示。

总结来说,数码管的驱动原理是通过控制数码管的各个灯段的开关状态来显示数字、字母或符号,并通过段选和位选的方式实现多个数码管之间的显示切换。同时,可以通过硬件电路或软件控制来实现数码管的驱动,并根据需要选择共阴极或共阳极数码管进行驱动。

注:本项目实际采用动态扫描显示驱动数码管。

5、指示灯

本项目额外设计了一个电源指示灯和IO工作指示灯。

由于芯片I/O往往灌电流的能力大于拉电流的能力,所以,LED1设计为I/O低电平有效(亮)。出于减少LED对电流的消耗的考量,放弃部分LED亮度,减少器件参数类型,将LED的限流电阻选择为10K。

以本项目所使用的插件F5白发白(白光)LED为例,下表是其电性参数,由表格参数可知,限流电阻的设置要保证电流在20mA以内。(欧姆定律算一下即可)

几个名词解释:

- 白发白LED:第一个白,即为白色或透明外壳,发白,LED发白光。此外还有 红发红 白发红等,白发红,即为白色或透明灯珠外壳的红光LED。

- F5:φ5 灯珠外壳直径D=5mm。市面上绝大多数F3/F4/F5的LED,引脚间距是一致的,均为P=100mil(2.54mm)。

从数码管和LED引申出的亮度问题思考

限流电阻和供电电压相同时,同一系列的不同颜色的LED(或数码管),亮度会有区别,这取决于不同颜色的LED对工作电压和工作电流需求的差异造成的。

6、按键电路设计

按键控制电路有多种设计方式,得益于CW32的I/O口内部可以配置上下拉电阻,在芯片外围的按键控制电路则无需配置。按键一端接入MCU的I/O上,另一端接地。按键按下,I/O被拉低。

7、用于电压测量校准的TL431电路设计

本项目额外增加了一个TL431电路用来提供一个2.5V的基准电压,可用于给芯片一个用于校准AD的外部电压基准。在开发板上设计此电路,用于学习相关应用原理。

由于我本人实际使用的是友台半导体的TL431封装TO-92,其产品手册为英文,所以找来TI公司的TL431产品的中文手册,方便大家学习理解。

TL431相关知识

TL431算是一个比较“老”的器件了,很经典,应用很广泛,现在在很多电子产品中仍然有其身影。

可能很多新手初次接触此器件,我们简单的讲讲此产品的原理,方便大家更好的应用TL431。

TI从名称上,将其定义为:精密可编程基准,我们在参考文献的第一页上,可以重点关注几个特性。

精密:精密,说明其输出电压非常准。我使用的为±0.5%精度的TL431,在室温下,板上实测2.495V。相较于常见的稳压二极管,精度天差地别。在应用电路图中,TL431内部以一个稳压管的符号做示意。 可调输出电压:可调输出电压在Vref到36V之间,我们在项目中使用输出Vref电压。Vref电压约为2.5V。所以我们在描述中用2.5V,实际是约等于的。 灌电流能力:也就是输出电压的引脚可以提供多少电流,这与在应用电路中的电阻(R13)的阻值有很大关系。不能低于1mA。如果没有灌电流的需求,则不要将电流设计过大,造成不必要的功耗影响。

TL431工作原理

理解TL431的工作原理,有益于快速理解其不同应用。

在TI的手册中找到功能方框图,我们仅需分析其等效原理图即可。

431的核心是一个运放,在电路中充当比较器。芯片内部有一个Vref电压(约为2.5V),作用在比较器的反相端。比较器的同相端会输入一个电压给REF,当这个电压大于Vref时,比较器输出高电平,使能三极管,使CATHODE(阴极)端与 ANODE(阳极)端导通,此时,若REF和CATHODE处于同一电位(连接在一起),则REF处的电位被拉低,当REF处的电位被拉低至低于Vref时,比较器输出低电平,三极管关断,REF处的电位回升,当高于Vref时,继续执行以上描述,如此循环。由于硬件的响应速度是极其快的。所以REF处的电压几乎等于Vref。

注:ANODE处的电位可以理解为GND 0V。

电阻R13的选型

在项目中,电阻R13的值 1K 是如何来的?

由于在本项目中,需要REF输出一个约2.5V的基准参考电压给MCU的ADC引脚,而MCU的ADC内部通常阻抗很大,所以对REF引脚没有灌电流需求,灌电流设置应当减小,但不可小于1mA。以1mA为例计算:

根据基尔霍夫电流定律,通过REF的电流忽略不计,则电流全部穿过TL431。

根据欧姆定律:R13=(5V-2.5V)÷1mA = 2.5KΩ

实际项目使用1k电阻,减少使用电阻的料号。将灌电流设置为:I=2.5mA

R13还能再选小一些吗?可以,但是不推荐,因为不必要的电流流入TL431,会造成器件发热,产生不良影响。

拓展:TL431输出电压带载

根据基尔霍夫电流定律,通过R13(以R13为例)的电流等于通过REF和431的电流之和。

由于TL431最大能承受100mA的电流,而负载的电流可能是动态变化的。所以,流经R13的电流不得超过100mA,此外为保证431正常工作,流经431的电流不得小于1mA,即TL431应用为驱动不大于99mA的负载。

实际应用的计算用初中所学欧姆定律即可。

以100mA为例,计算得出R13=(5V-2.5V)÷100mA = 25Ω 。

此时应注意电阻的功率选型,

此时功率 P=UI=2.5V * 100mA = 0.25W

所以应当选择大于0.25W功率封装的电阻,即至少选用0.5W功率封装的电阻。

拓展:TL431输出任意电压

前文提到,TL431可以输出2.5V~36V的电压,那他是怎么实现的呢?

TI在手册中给了相应的原理图作为参考:

根据公式:Vref=R2/(R1+R2) *Vout

Vref已知,R1、R2由我们在电路中设计,可以得出输出电压Vout

根据基尔霍夫电流定律,由于实际电路中流经R1的电流要大于流经R2的电流(流入REF),如需精确计算,应当把多余未计算的电流产生的电压一并算入。

基准输入电流Iref已在手册的电气特性中给出(图为示例):

拓展:电阻器选型的注意事项

除了上文所讲的一些电阻器选型问题外,还要额外就这个项目说明一下电阻器的选型细节。

本项目涉及到AD采样等,需要通过欧姆定律等公式带入电路中的电阻阻值。在实际电路中,电阻的阻值并不是就绝对等于我们原理图所标注的那样,并且, 电阻的阻值通常会随着温度的变化而变化。这种变化称为电阻的温度系数。不同类型的电阻器具有不同的温度系数。

为了便于项目调试与学习,在平衡成本与精度的考量下,本项目的全部电阻均使用1%精度电阻(百一)。由于使用的是插件的金属膜电阻,除了电流采样电阻R0外,均使用1/8W功率封装。 电阻一般精度越高,价格越贵,实际本项目一些地方的电路设计,电阻使用百五精度即可。